© 2024 EasyEDA Some rights reserved ISO/IEC

Editor Version

×

Standard

1.Easy to use and quick to get started

2.The process supports design scales of 300 devices or 1000 pads

3.Supports simple circuit simulation

4.For students, teachers, creators

Profession

1.Brand new interactions and interfaces

2.Smooth support for design sizes of over 5,000 devices or 10,000 pads

3.More rigorous design constraints, more standardized processes

4.For enterprises, more professional users

Ongoing

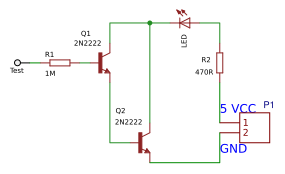

STD Punta logica con 2 transistores

License: Public Domain

Mode: Editors' pick

- 0

Update time:

2021-04-09 17:04:49

Creation time:

2016-06-07 00:47:43

Description

Descripción

Circuito muy sencillo que muestra la implementación de una punta lógica con dos transistores bipolares NPN en conexión Darlington. Ese circuito encenderá el diodo led cuando en su entrada haya un “1” lógico y lo apagará cuando haya un “0” lógico. La fuente de 5 voltios que se utiliza puede ser la misma fuente que alimenta el circuito lógico bajo prueba.

La punta de prueba lógica no cargará el circuito bajo prueba debido a la resistencia de 1 megaohm que esta en serie con la punta y alta impedancia de tienen los dos transistores en conexión Darlington.

La utilización de una configuración Darlington permite que una pequeña corriente de entrada pueda encender un LED sin problemas. El beta (b) de un transistor 2N2222a es de al menos 100, eso significa que los dos transistores en configuración Darlington tendrán una ganancia de 100 x 100 = 10 000, mínimo.

Este circuito, debido a sus pocos elementos, se puede implementar en un impreso delgado en forma de lapicero para su fácil utilización.

A continuación se presentan un circuito impreso sugerido para implementar esta punta lógica y un diagrama con un estimado del resultado final. Al circuito impreso hay que ponerle una punta metálica conectada al punto P, para que sirva como punta de prueba. Al terminal CN!, se conecta la alimentación del circuito. Aquí se pueden colocar dos cables: rojo para el positivo y negro para el cable que va a tierra, cada uno de ellos con terminal tipo lagarto para conectarse a la fuente de poder del circuito bajo prueba o para conectar una fuente externa.

Design Drawing

schematic diagram

(

1

/

)

PCB

(

1

/

)

The preview image was not generated, please save it again in the

editor.

| ID | Name | Footprint | Quantity |

|---|---|---|---|

| 1 | 2N2222 | TO18 | 2 |

| 2 | 1M | 02045 | 1 |

| 3 | 470R | 02045 | 1 |

| 4 | LED | LED5MM | 1 |

| 5 | SIP2 | HDR1X2 | 1 |

Unfold

Project Members

Related Projects

Change a batch

Loading...

Add to album

×

Loading...

reminder

×

Do you need to add this project to the album?