© 2024 EasyEDA Some rights reserved ISO/IEC

Editor Version

×

Standard

1.Easy to use and quick to get started

2.The process supports design scales of 300 devices or 1000 pads

3.Supports simple circuit simulation

4.For students, teachers, creators

Profession

1.Brand new interactions and interfaces

2.Smooth support for design sizes of over 5,000 devices or 10,000 pads

3.More rigorous design constraints, more standardized processes

4.For enterprises, more professional users

Ongoing

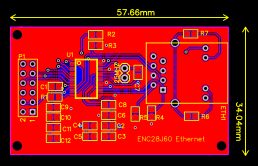

STD ENC28J60 Ethernet Board

Mode: Editors' pick

- 13

Update time:

2022-03-10 04:27:49

Creation time:

2015-10-27 01:22:54

Description

ENC28J60 Ethernet Project

Stand-Alone Ethernet Controller with SPI Controller.

Ethernet Controller Features

• IEEE 802.3 compatible Ethernet controller

• Integrated MAC and 10BASE-T PHY

• Supports one 10BASE-T port with automatic

polarity detection and correction

• Supports Full and Half-Duplex modes

• Programmable automatic retransmit on collision

• Programmable padding and CRC generation

• Programmable automatic rejection of erroneous

packets

• SPI Interface with clock speeds up to 20 MHz

Buffer

• 8-Kbyte transmit/receive packet dual port SRAM

• Configurable transmit/receive buffer size

• Hardware-managed circular receive FIFO

• Byte-wide random and sequential access with

auto-increment

• Internal DMA for fast data movement

• Hardware assisted checksum calculation for various network protocols

Medium Access Controller (MAC)

Features

• Supports Unicast, Multicast and Broadcast

packets

• Programmable receive packet filtering and

wake-up host on logical AND or OR of the

following:

- Unicast destination address

- Multicast address

- Broadcast address

- Magic Packet™

- Group destination addresses as defined by

64-bit hash table

- Programmable pattern matching of up to

64 bytes at user-defined offset

Physical Layer (PHY) Features

• Loopback mode

• Two programmable LED outputs for LINK, TX,

RX, collision and full/half-duplex status

Operational

• Six interrupt sources and one interrupt output pin

• 25 MHz clock input requirement

• Clock out pin with programmable prescaler

• Operating voltage of 3.1V to 3.6V (3.3V typical)

• 5V tolerant inputs

• Temperature range: -40°C to +85°C Industrial,

0°C to +70°C Commercial (SSOP only)

• 28-pin SPDIP, SSOP, SOIC, QFN packages

1.0 OVERVIEW

The ENC28J60 is a stand-alone Ethernet controller

with an industry standard Serial Peripheral Interface

(SPI). It is designed to serve as an Ethernet network

interface for any controller equipped with SPI.

The ENC28J60 meets all of the IEEE 802.3 specifications. It incorporates a number of packet filtering

schemes to limit incoming packets. It also provides an internal DMA module for fast data throughput and hardware assisted checksum calculation, which is used in

various network protocols. Communication with the host controller is implemented via an interrupt pin and the SPI, with clock rates of up to 20 MHz. Two dedicated pins are used for LED link and network activity

indication.

A simple block diagram of the ENC28J60 is shown in

Figure 1-1. A typical application circuit using the device

is shown in Figure 1-2. With the ENC28J60, two pulse

transformers and a few passive components are all that

is required to connect a microcontroller to an Ethernet network.

The ENC28J60 consists of seven major functional

blocks:

1. An SPI interface that serves as a communication channel between the host controller and the

ENC28J60.

2. Control Registers which are used to control and

monitor the ENC28J60.

3. A dual port RAM buffer for received and

transmitted data packets.

4. An arbiter to control the access to the RAM

buffer when requests are made from DMA,

transmit and receive blocks.

5. The bus interface that interprets data and

commands received via the SPI interface.

6. The MAC (Medium Access Control) module that

implements IEEE 802.3 compliant MAC logic.

7. The PHY (Physical Layer) module that encodes

and decodes the analog data that is present on

the twisted pair interface.

The device also contains other support blocks, such as

the oscillator, on-chip voltage regulator, level translators

to provide 5V tolerant I/Os and system control logic.

Design Drawing

schematic diagram

(

1

/

)

PCB

(

1

/

)

The preview image was not generated, please save it again in the

editor.

| ID | Name | Designator | Footprint | Quantity |

|---|---|---|---|---|

| 1 | ENC28J60 | U1 | SSOP28DB | 1 |

| 2 | 1u | C1,C2,C3,C4,C5,C6,C9,C10,C11,C12 | C0805 | 10 |

| 3 | 1k | R1,R2,R3,R4,R5,R6,R7 | C0805 | 7 |

| 4 | XTALfast | 25MHZ | 1X02 | 1 |

| 5 | 20p | C7,C8 | C0805 | 2 |

| 6 | HDR2X6 | P1 | HDR2X5 | 1 |

| 7 | CON-RJ45-F | ETH1 | HR911105A | 1 |

Unfold

Project Members

Related Projects

Change a batch

Loading...

Add to album

×

Loading...

reminder

×

Do you need to add this project to the album?