This guide is relevant if you want the following:

* panelize a PCB design, and

* have a ground plane (copper fill)

* use SMT assembly at JLCPCB

It covers a shortcoming (unsuitable for ground plane (copper fill)) of [https://docs.easyeda.com/en/PCB/Panelize/index.html#Panelize-by-Manually](https://docs.easyeda.com/en/PCB/Panelize/index.html#Panelize-by-Manually)

I wrote this guide so I don't have to reinvent the wheel next time I need one. I have sucessfully used it and confirmed that the PCBs ordered with assembly work as I intended. However, I will not take any responsibility for the correctness of this guide. USE AT YOUR OWN RISK. Based on at least one EasyEDA hack/bug, so it may cease to work with newer versions. Tested on V6.3.43.

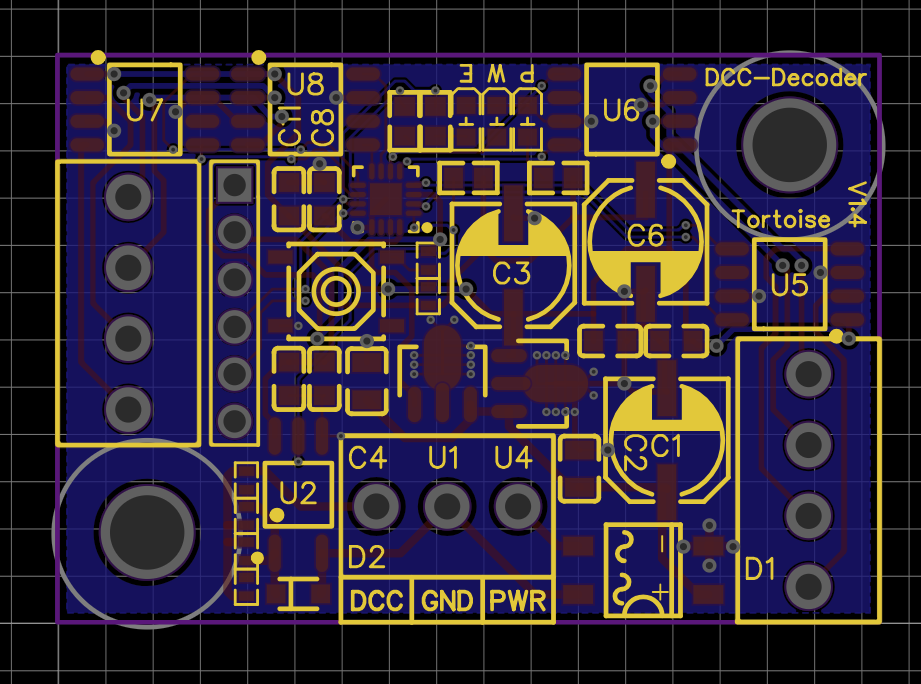

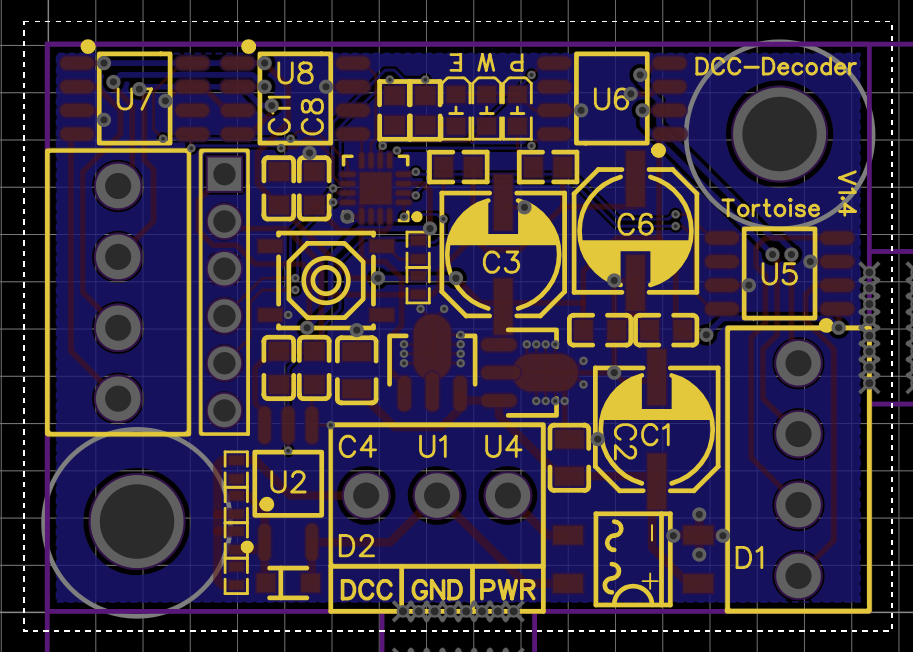

1\. Fully design and finish your single board\, including DRC\.

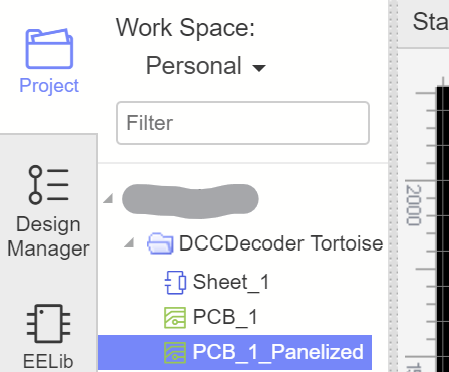

2\. Clone PCB design to new file \(named XY\_Panelized\) in same project\.

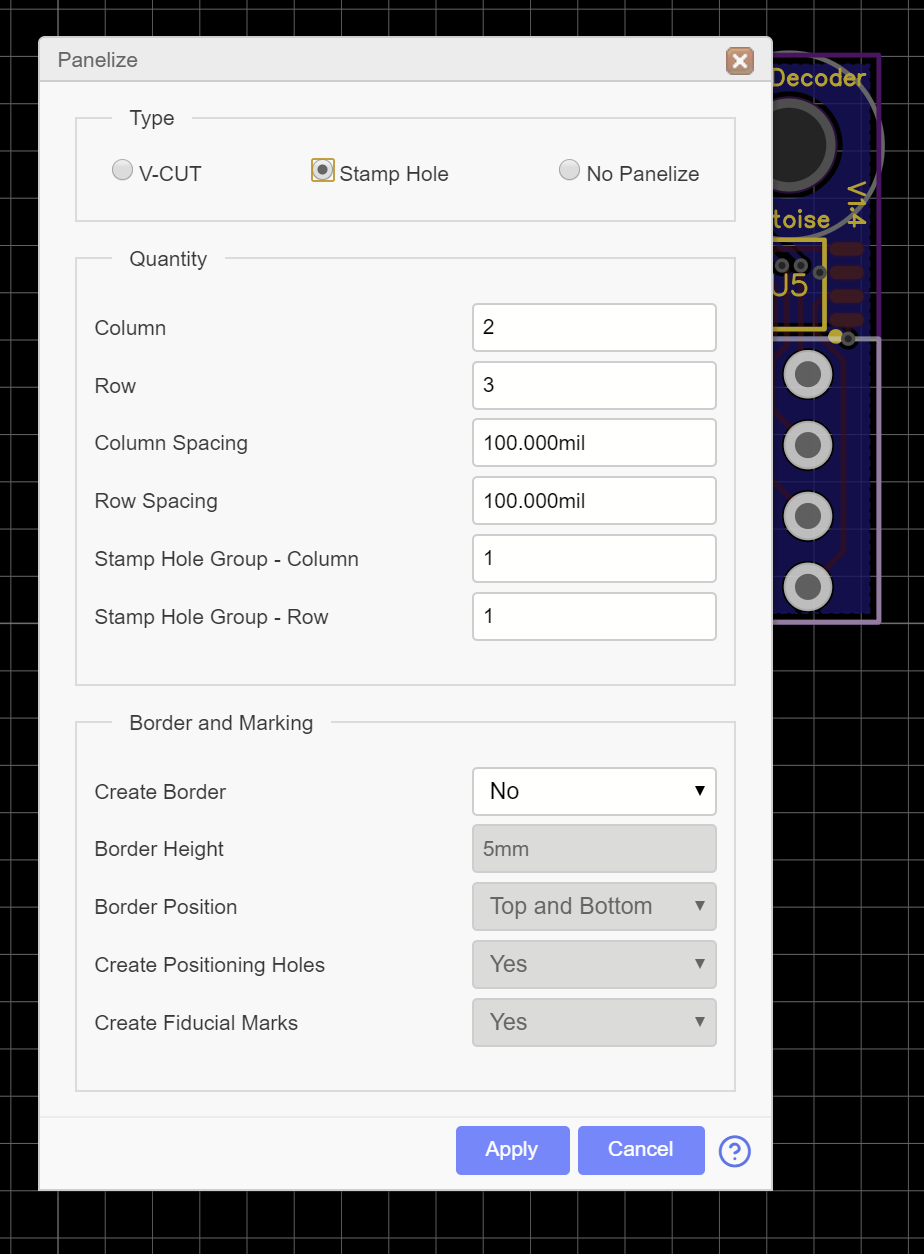

3\. Use the built\-in "Panelize" function to initially panelize the board\.

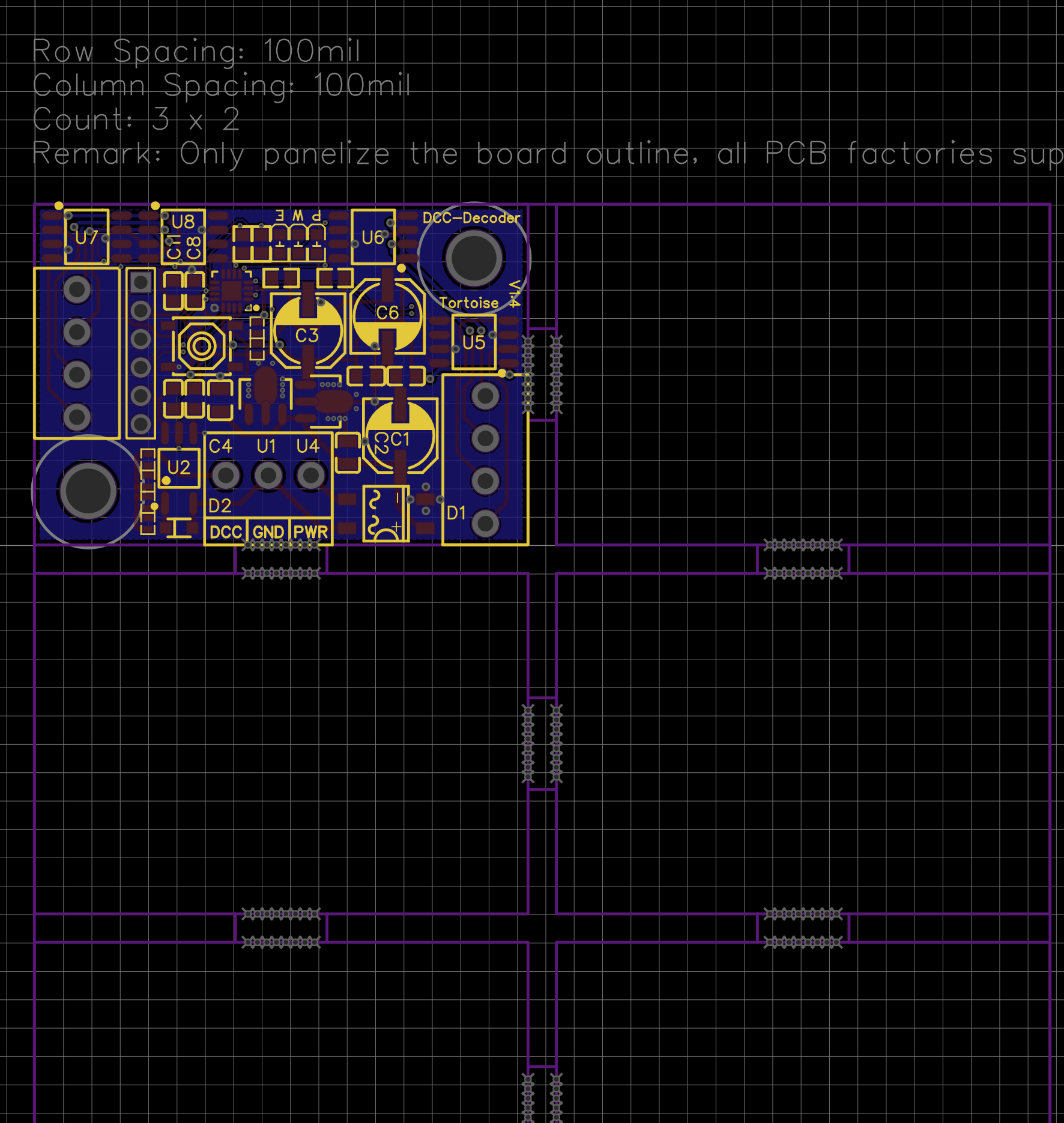

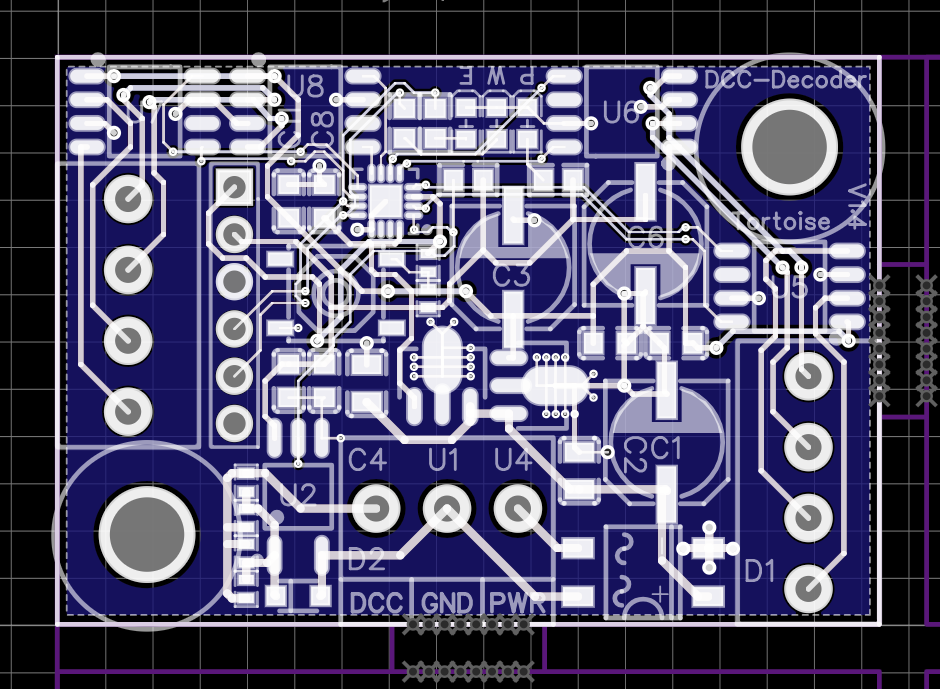

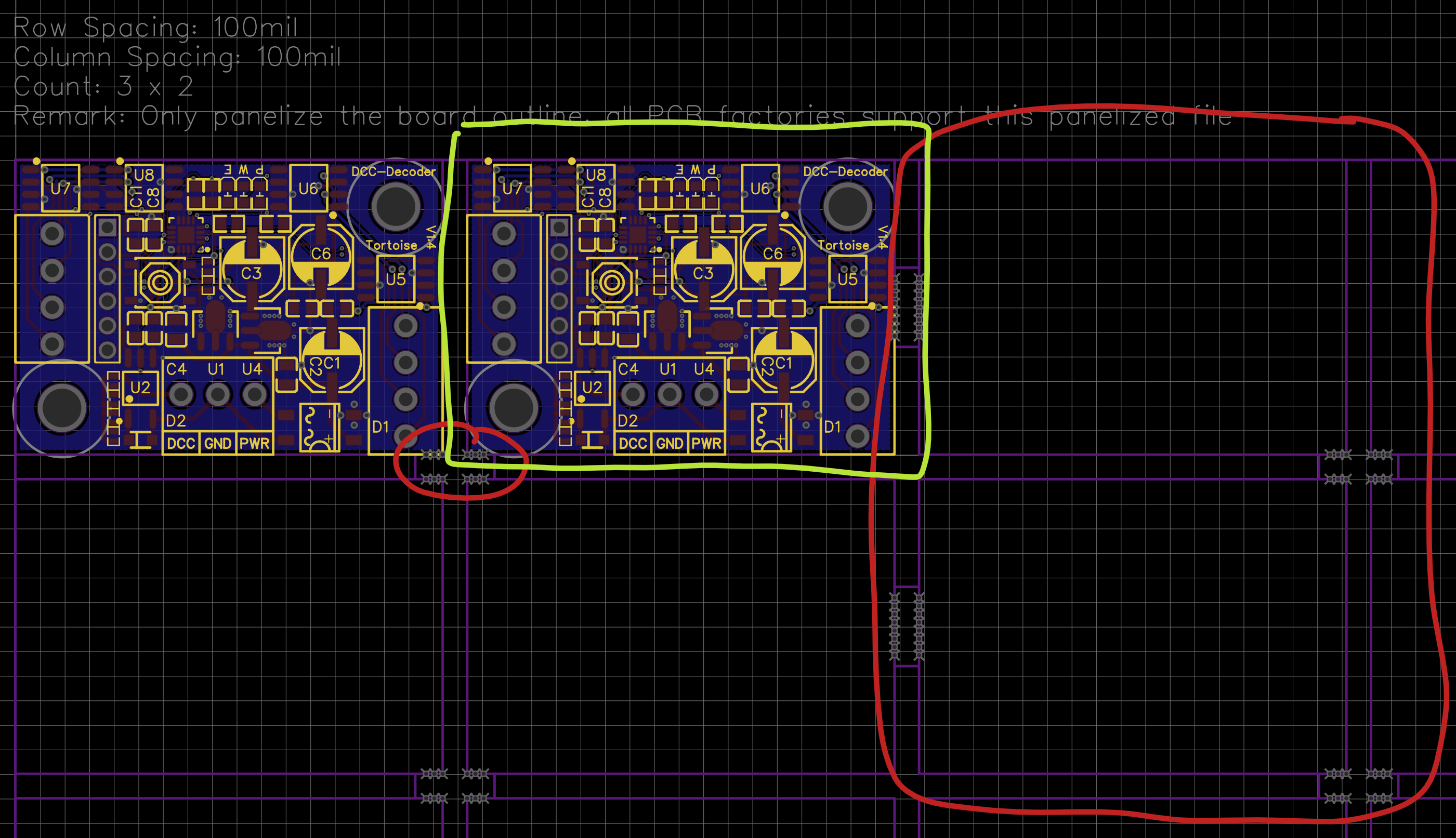

Note that only the outline is panelized. All the components and layout are not copied. Let's call the upper left board that has all the components and layout the "primary board".

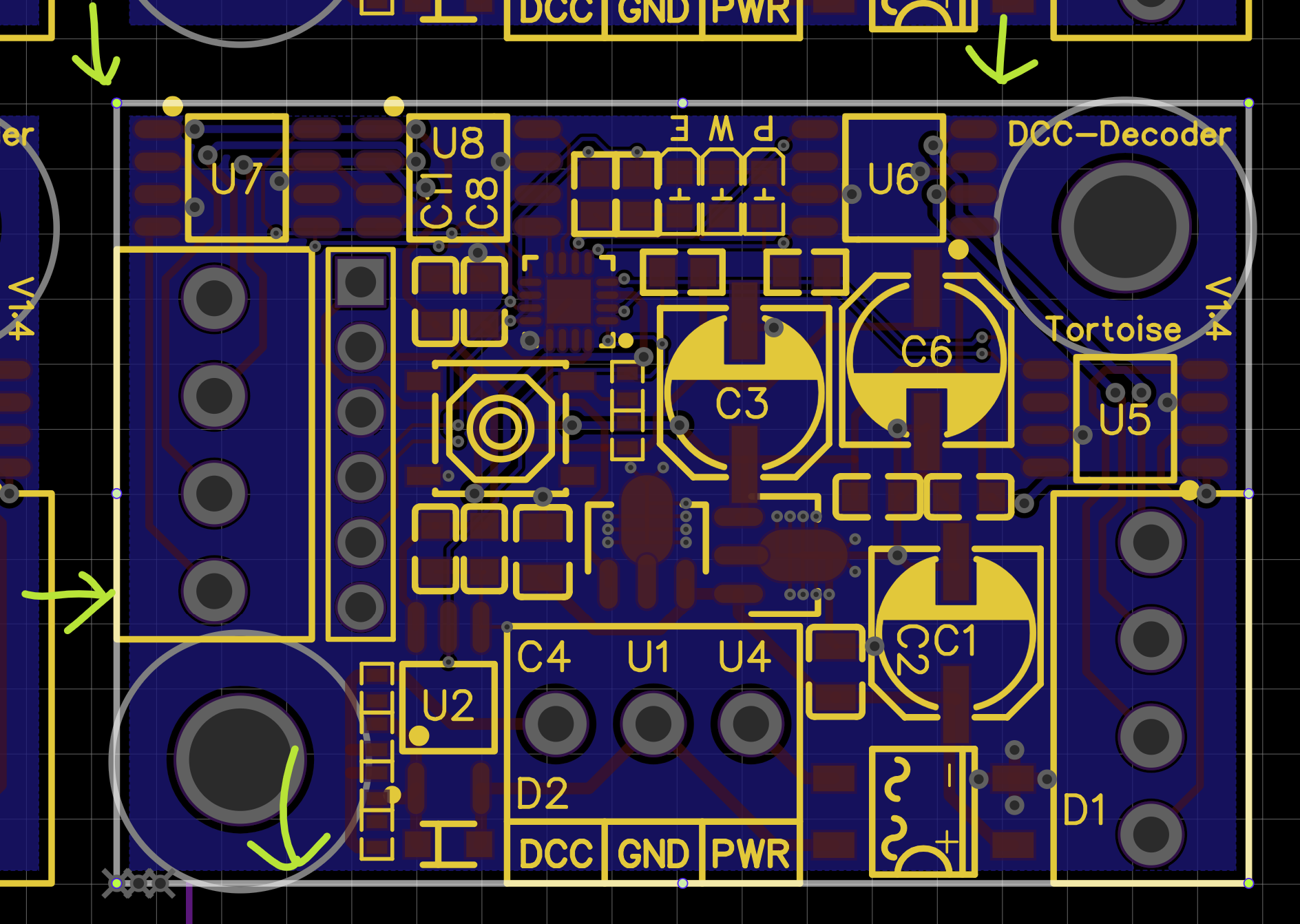

4\. Clone the primary board to all secondary boards\. Select the complete primary board including outline\.

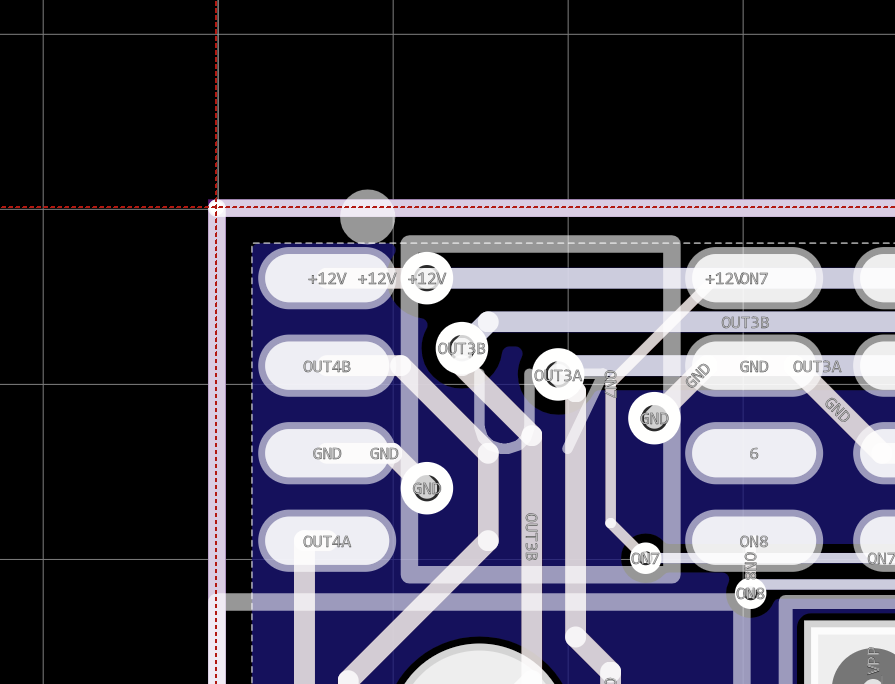

6\. Use Ctrl\+Shitf\+C to copy by reference point\. Use the upper left corner as reference point\. Make sure you hit the corner of the primary board outline exactly\, zoom in as needed\.

7\. Use Ctrl\+Shift\+V to paste by reference point\. Again\, make sure that you hit the corner of the secondary board exactly\.

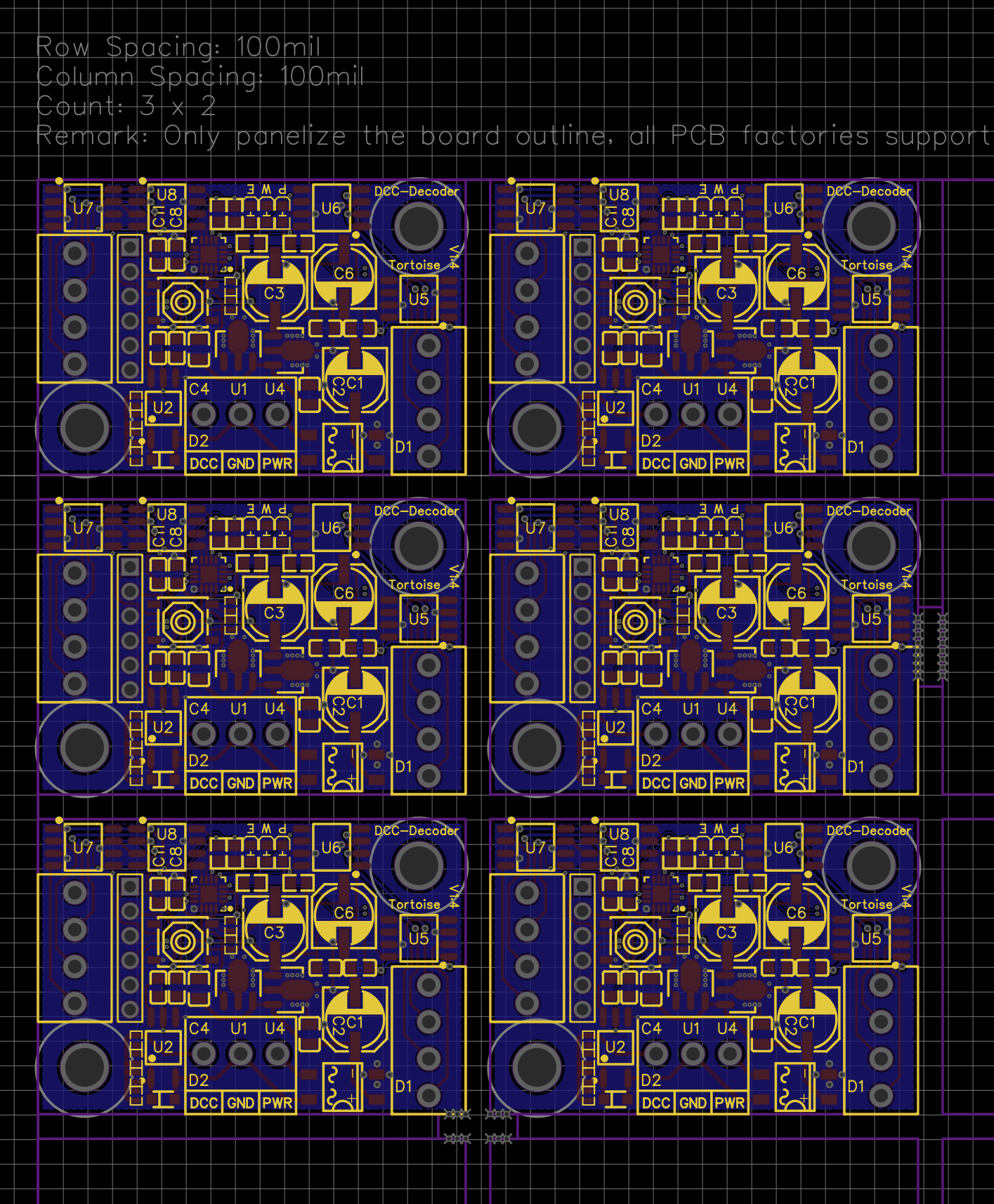

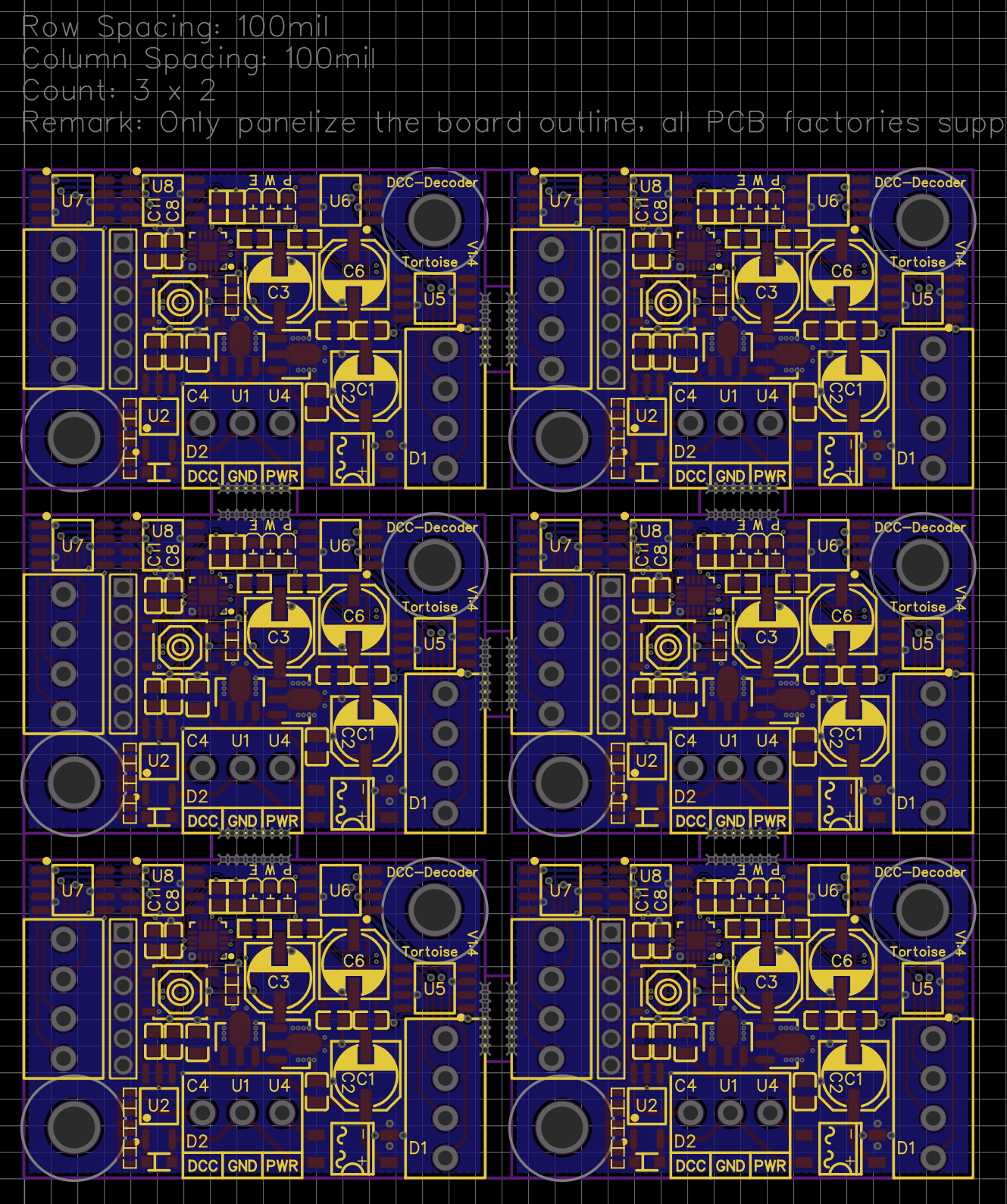

8\. If everything is done correctly\, all of the primary board including the copper area is copied\. Note that since we enabled panelization \*and\* we also copied the outline of the primary board\, the panelization will be extended and look wrong\. We will fix this later\. \(Copying outline in this step is \*required\* because otherwise the copper area will not copy correctly\!\)

9\. Repeat as needed until all secondary boards are copied\.

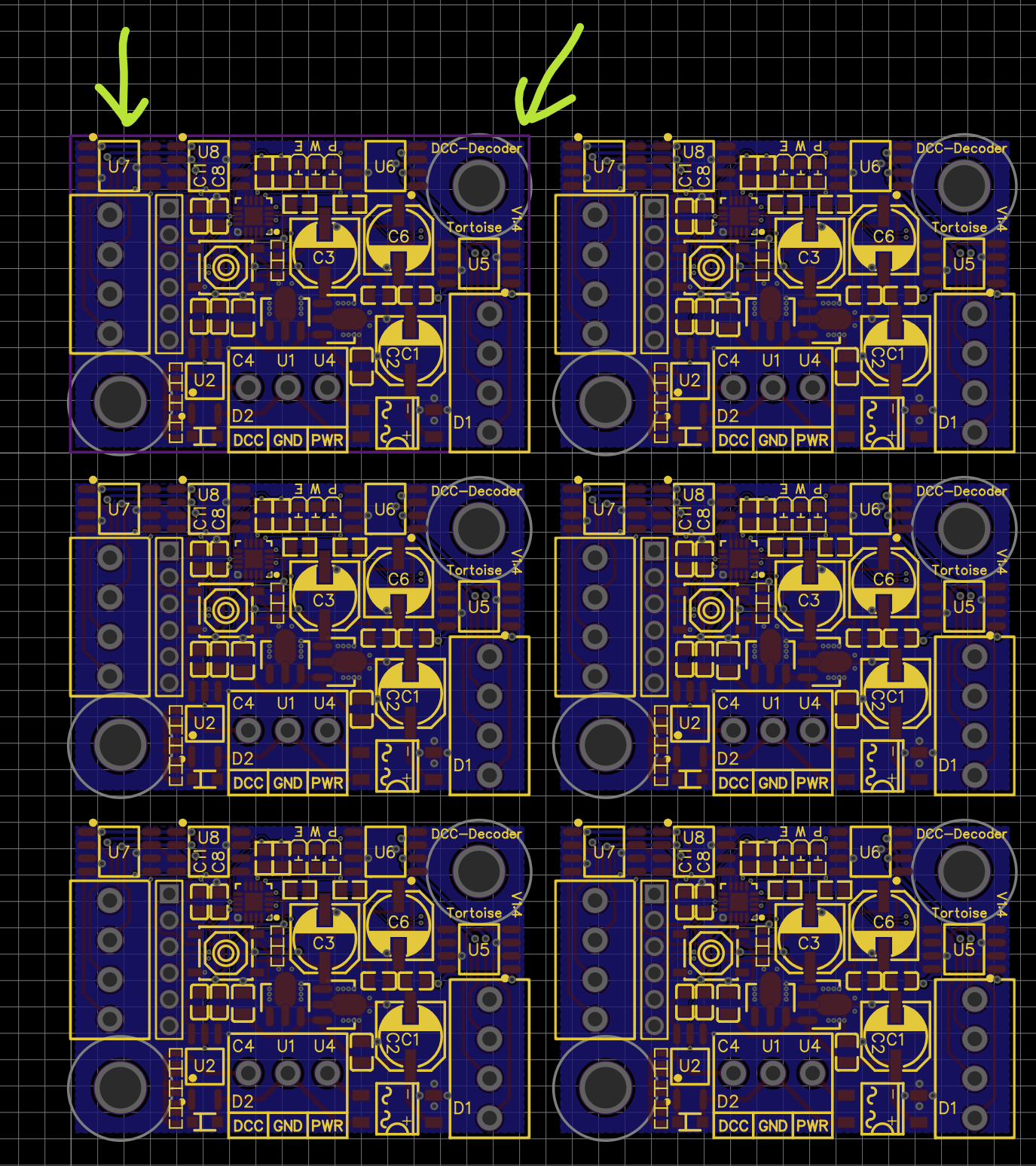

10\. Now we can fix the panelized outline\. For every secondary board\, select and delete the outline\. \(This will NOT delete/destroy the ground plane and is\, in essence\, why this guide works\!\)

11\. Open the Panelize Dialog and set to "No Panelize"\. All of the purple lines should be removed except for the primary board outline\. This will clean up the outline mess that we made\.

12\. Then re\-enable panelization\, with the exact same settings as before\.

13\. You should now have a panelized board that a\) includes all components and layout on all sub\-boards b\) includes the ground plane for all sub boards and c\) has the correct outline for you panel\, including stamp holes\. You can generate gerber files for the panel and upload to JLCPCB\.

Firefox

75.0

Windows

10

EasyEDA

6.3.43