Hi there,

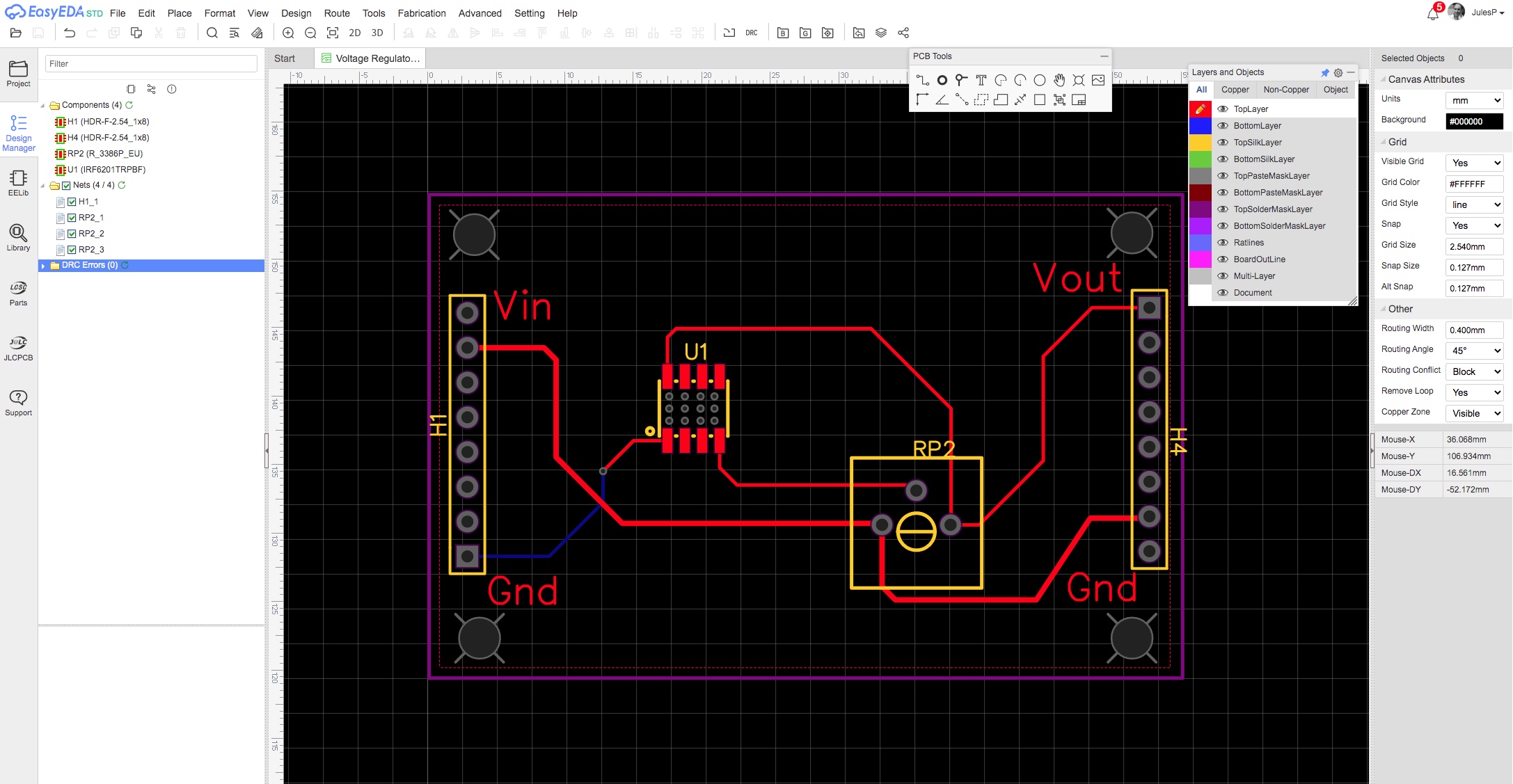

I have a query about the best way to assist heat transfer away from a MOSFET that is likely to get quite hot. The simple circuit involves an IRF6201 with its small SOIC-8 package with which I will add a heat sink on top. However, I also wish to add some vias within the area of the footprint, as can be seen in the image.

My approach is to lay out a grid of 9 vias within the main IC footprint and then do a GND Copper Pour which should allow heat to flow from the underside of the chip to the large copper area.

Firstly, when I did the Copper Pour I could not get it so show despite it being 'Visible' so it's hard to see the interaction with the vias. Secondly, is this the simplest way to assist heat transfer or should I add instead a Pad under the chip and put vias in that? I have read various forum posts on the topic but I end up being a little confused by all the detail.

Thanks

Chrome

87.0.4280.141

OS X

10_13_6

EasyEDA

6.4.14