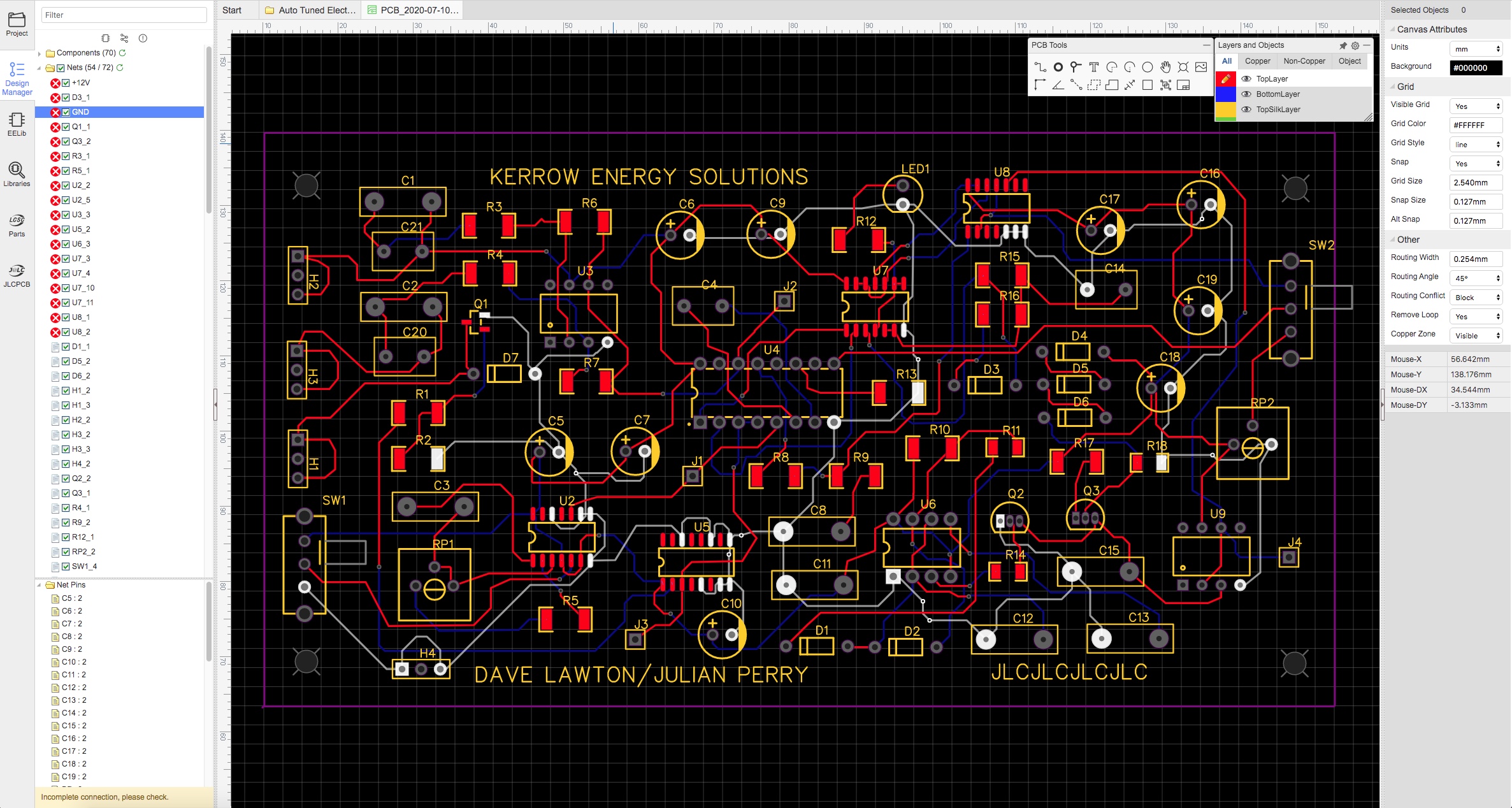

I have just completed a PCB design and did the circuit check before producing the Gerber files. It came up with a whole load of 'errors' based on 'incomplete connections'.

I don't understand this as all the connections are as the schematic says and, in the case of the highlighted GND one, they all connect to each other and to the GND terminal at H4 in the lower left corner. What am I missing here or is this as assumed error based on a set of circuit assumptions?

Thanks

Jules

Electron

7.1.14

OS X

10_13_6

EasyEDA

6.3.53