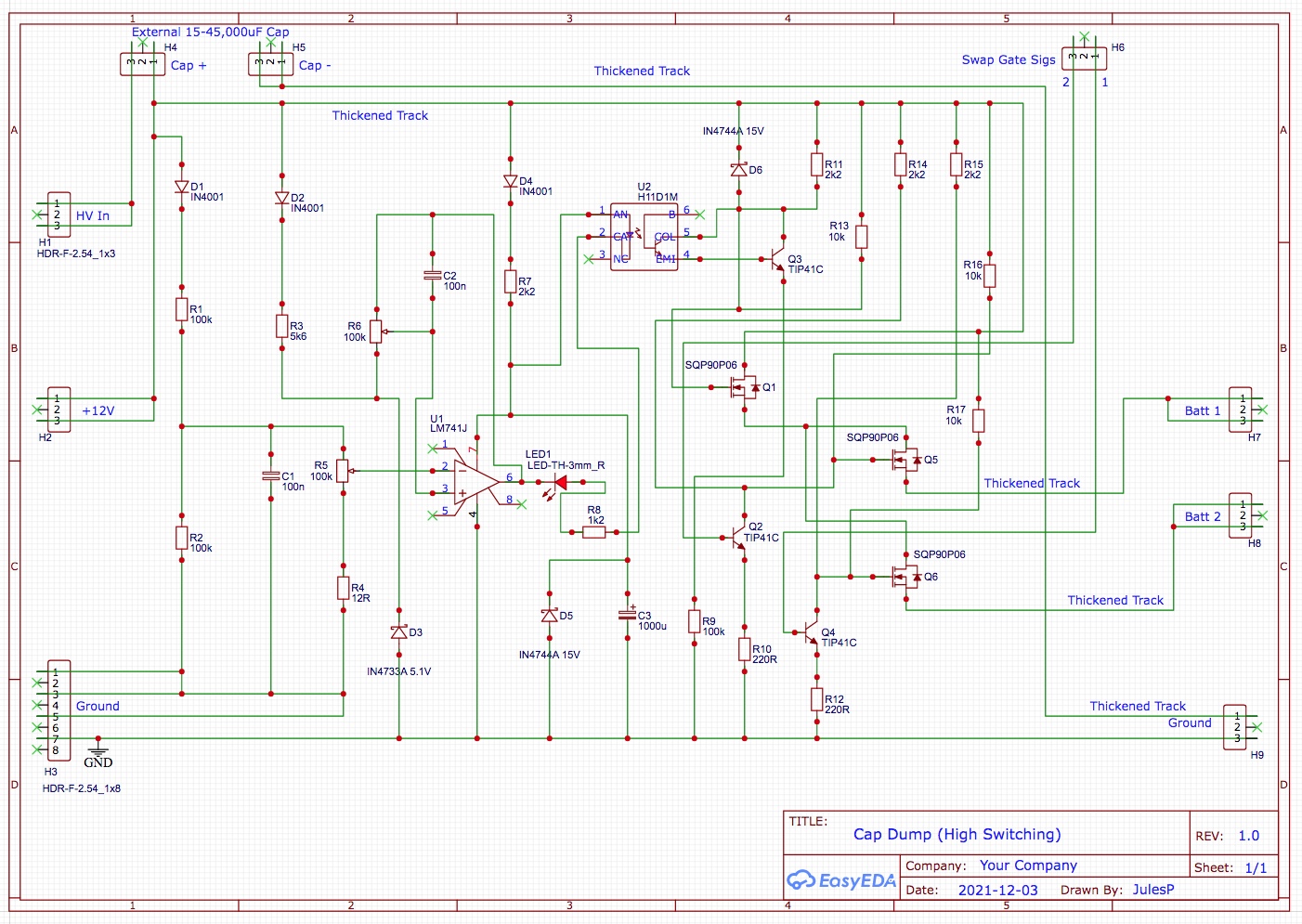

I have a query regarding the solder tracks on a PCB that I have designed (attached).

Due to high pulse currents from a capacitor, of the order of 50-120A, some of the tracks on the PCB will need to be enhanced by, if possible, adding solder to a regular track of say 4-5mm width. I don’t know what the current carrying capacity of such tracks is so maybe you have some data on this for different track dimensions of standard thickness?

Besides that, do you also know if the protective resin layer on the top of a PCB will melt away with the heat of a soldering iron so I can add extra solder, or if it will resist such heat and prevent me from thickening the track?

Thanks,

Jules

Chrome

96.0.4664.55

OS X

10_13_6

EasyEDA

6.4.25