Hello,

I got a big issue on my current project today, It's a shared project, my partner and I dont see the exact same project, the ground plane is not sync.

When rebuild ground plane, the PCB tab is not marked as "*" (need to save). Also DRC dont catch the bridge and my real PCB goes to trash :(

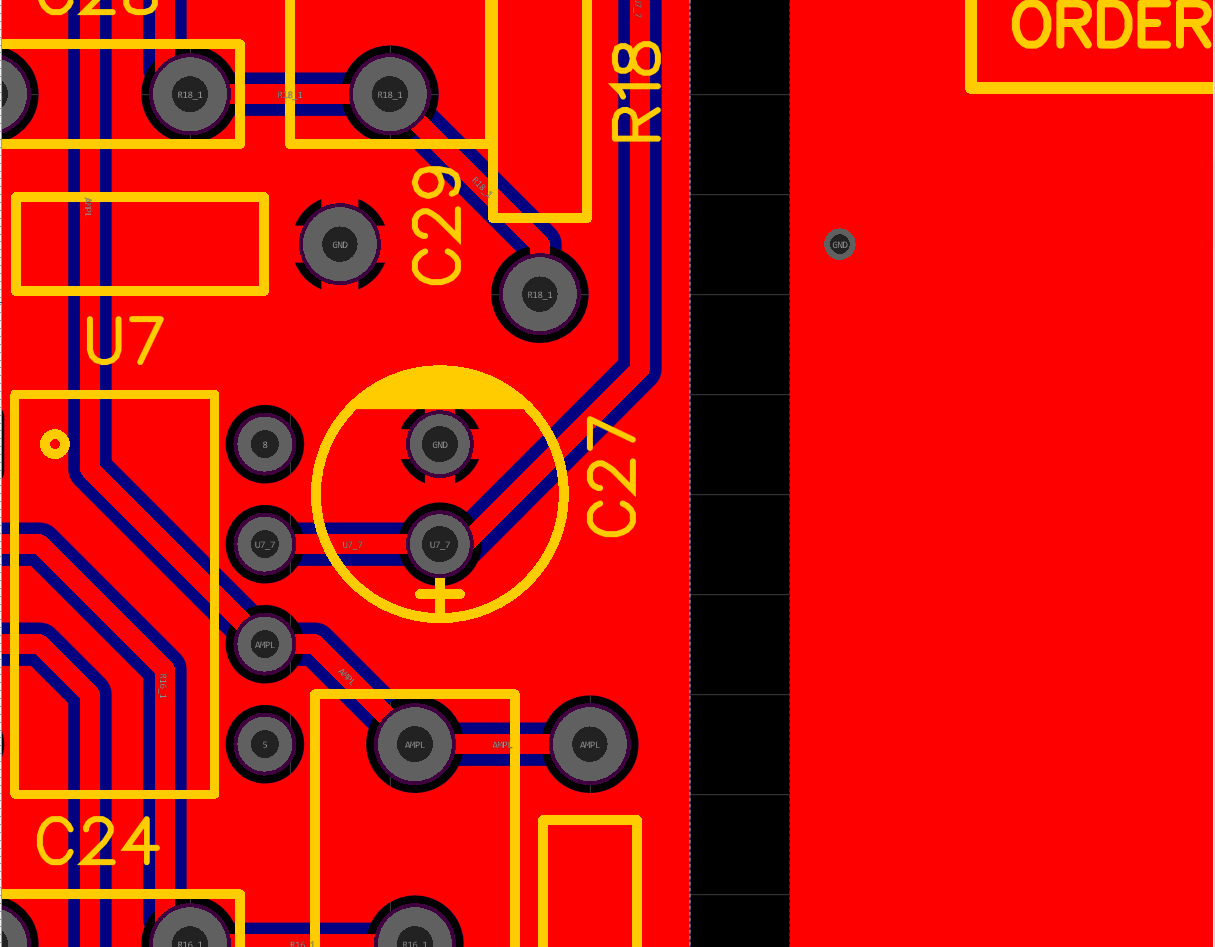

**What my partner see :**

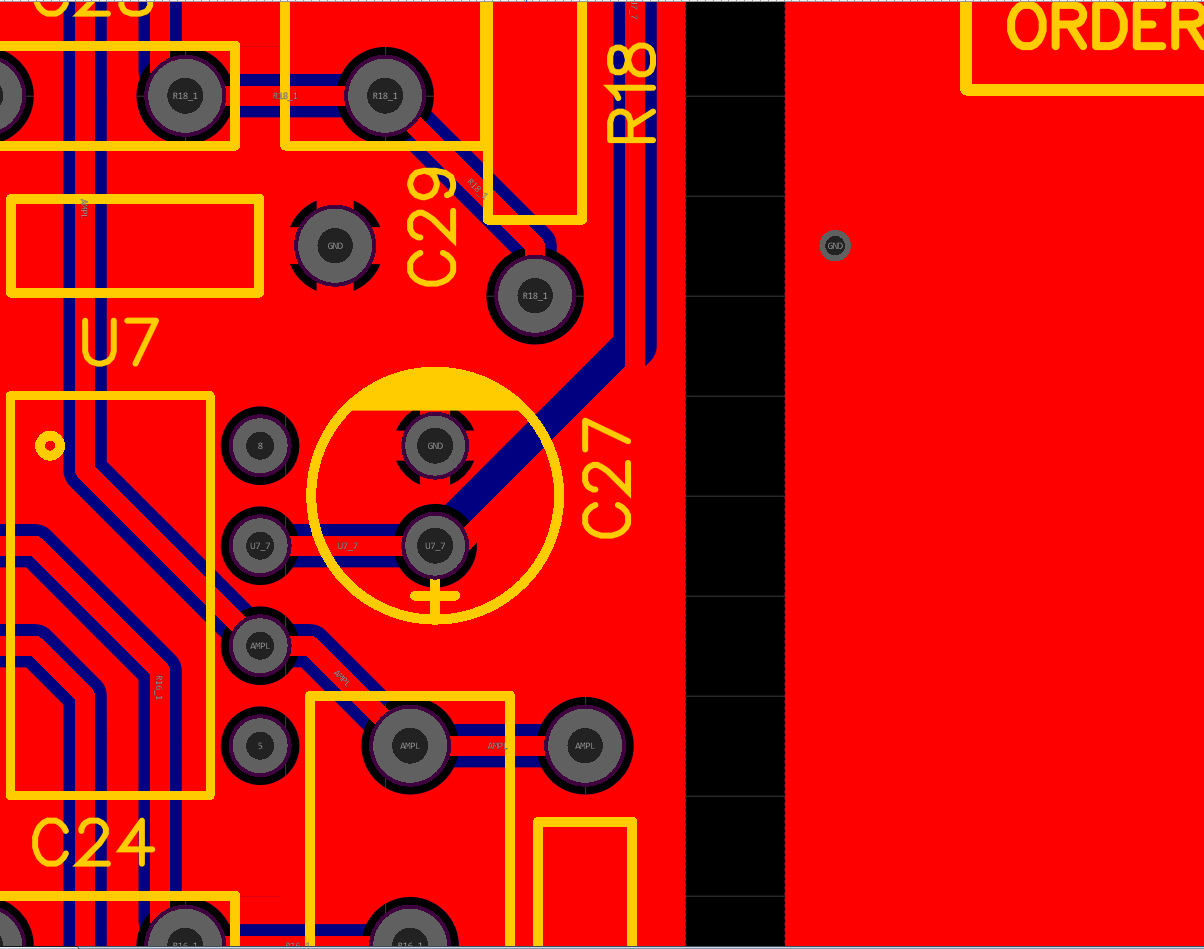

## What I see

As you see U7\_7 is short circuit to ground plane\. I dont know why project is not sync only on ground plane\.\.\.I dont know why DRC dont catch this \(Gound plane NET is GND\, whyt DRC let connect to U7\_7\)\.\.\.

I always check my file before production, I always rebuild ground plane before production and I always check DRC before production, I dont understand how this can append. The desync disturbing me

This scarry me !

Firefox

65.0

Windows

7

EasyEDA

5.9.42