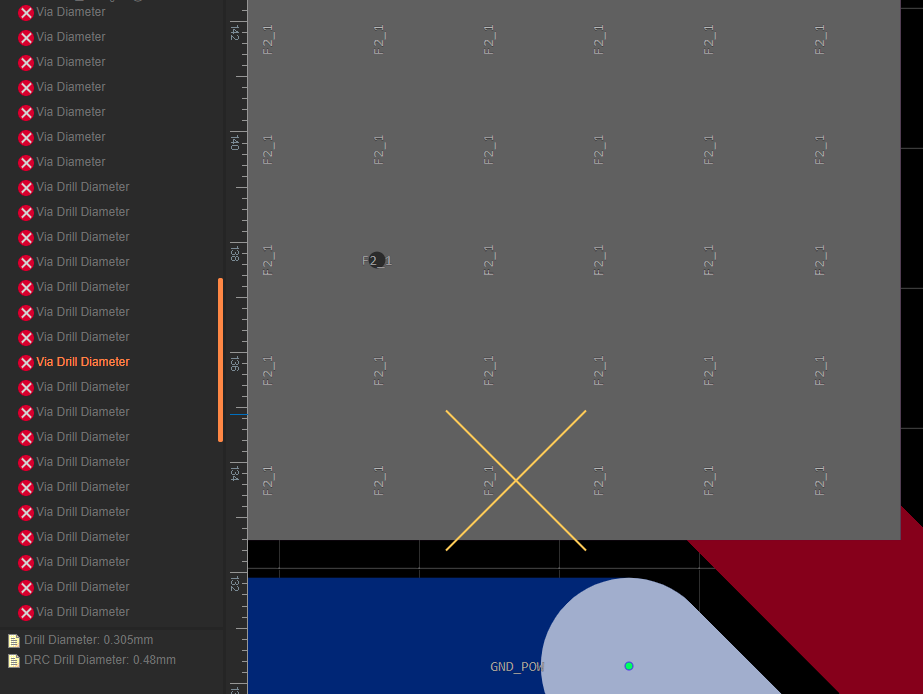

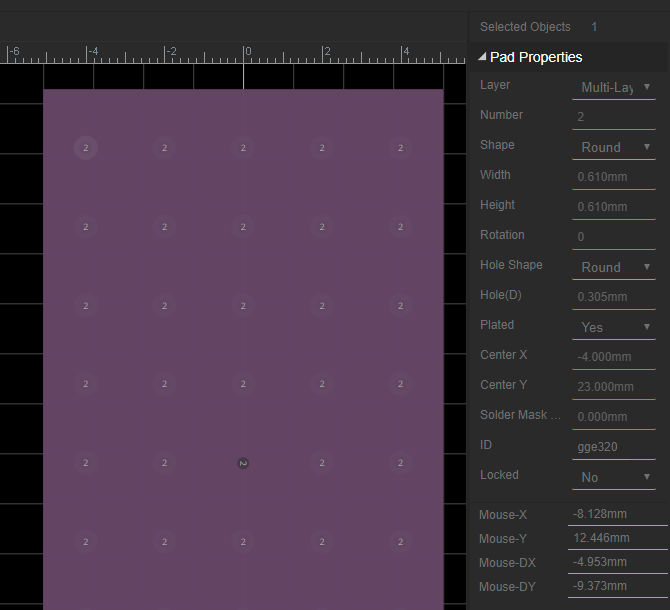

I wanted an area for a TO-220 component to be soldered to the PCB and cooled. I modified a footprint to include one really large rectangular pad and put lots of small circular pads inside it (diam 0.61 mm, hole 0.305 mm). I updated the footprint of my component in the schematic and updated the PCB to include the modified footprint. The pads are identified as vias and trigger the DRC, even though they were created as pads and shouldn't need to obey the design rules for vias because a) they're for heat, not power and b) there's 45 of them anyway (generating 90 DRC errors).

For some reason the PCB view doesn't show the holes in the centre of the thermal pads even though the holes are present in the 3D view.

I think EasyEDA should just add a feature for making thermal vias which are exempt from the normal rules for connections and diameter etc.

[https://easyeda\.com/editor\#id=\|bceeb9c3354e4eefb7b1aebc1d7b3105\|53b8858434d0471e8478ad83bd7a6130\|beacd93fad4a40a3b592bb6dc4595450](https://easyeda.com/editor#id=|bceeb9c3354e4eefb7b1aebc1d7b3105|53b8858434d0471e8478ad83bd7a6130|beacd93fad4a40a3b592bb6dc4595450)

Firefox

92.0

Windows

10

EasyEDA

6.4.25