Hi

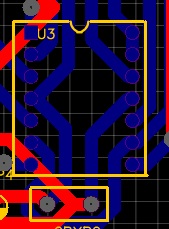

Is there a way to design a pcb lib package that has bottom only layer connections but the component itself will sit on the top? The problem is if you set all the connections just to bottom the auto router will place tracks across the components connections on the top layer. This is fine for smd components but doesn't work for something like a pdip carrier socket where the connections are always onto the bottom layer but the socket itself is sitting on the top layer and has connections through the pcb. To illustrate see pin 7 (bottom left) in the attached. All the sockets connections have been set to the bottom but a track is going through pin 7 on the top effectively giving a connection between the top and bottom layers where it shouldn't.

A similar problem occurs with the auto router if you mark connections to an ic in a schematic as n/c. The auto router then believes its fine to place a track through the n/c pin when in reality although the circuit design may purposely have no connection internally inside the ic the pin may actually do something! The work around is not to mark pins as n/c in the schematic but that makes having a n/c element pretty pointless.

Chrome

72.0.3626.119

Windows

10

EasyEDA

5.9.42