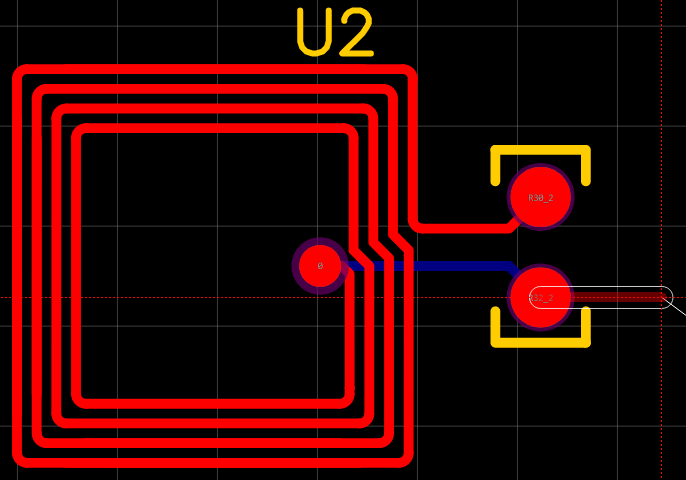

I am currently adding an NFC antenna to my board. However, I cannot connect one of the pads of my antenna to the corresponding component.

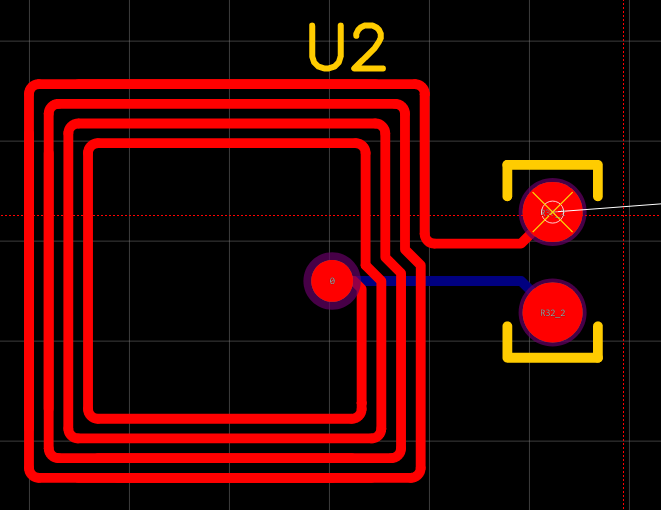

Indeed, when I want to connect the top pad of this antenna, a yellow cross appears, while it works for the bottom pad. However, I have associated the antenna schematic to the footprint. Can you help me ?

Click [here](https://easyeda.com/component/5ebdd721e2a3421f97ebfb3d06dd969f) to see my component:

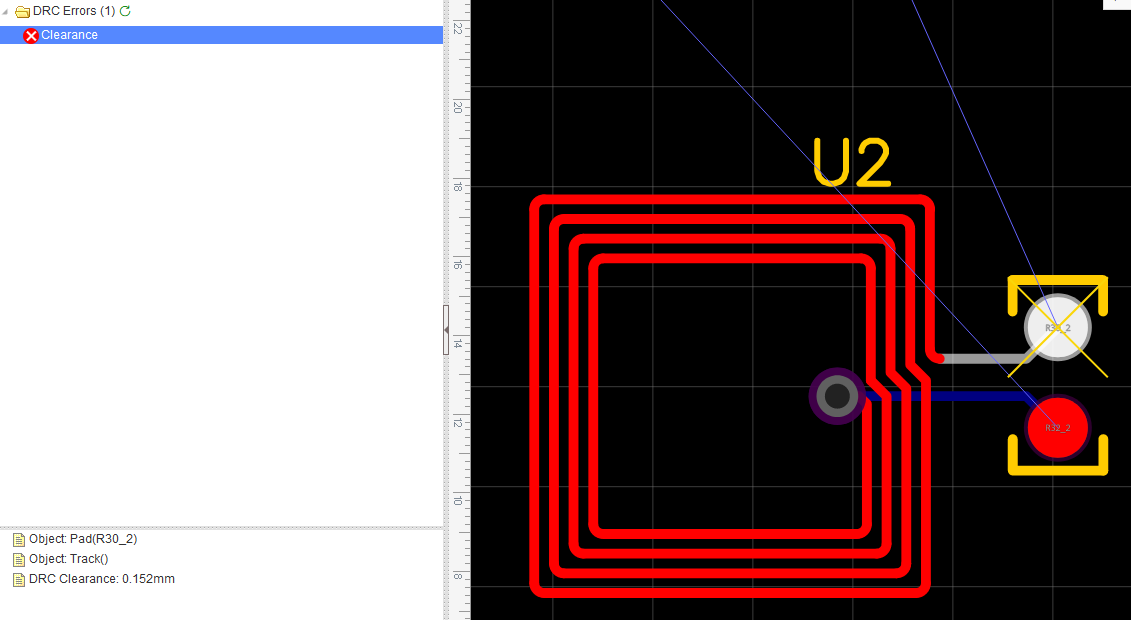

Here is the DRC error I get:

Firefox

85.0

Windows

10

EasyEDA

6.4.14